INTEGRATED CIRCUITS

Objective specification File under Integrated Circuits, IC17 2000 Feb 17

# **UAA3535HL**

## FEATURES

- Multi-band application for GSM, DCS and PCS cellular phone systems

- · Low noise and wide dynamic range low IF receiver

- More than 35 dB on-chip image rejection in receive mode

- More than 64 dB gain control range in receive mode

- Integrated channel filter

- Integrated TX low-pass filter

- High precision I/Q modulator

- Multi-band TX modulation loop architecture including offset mixer and phase-frequency detector

- · Dual PLL with on-chip fully integrated IF VCO

- Fully differential design minimizing crosstalk and spurious signals

- Functional down to 2.4 V and up to 3.6 V

- 3-wire serial bus interface

- LQFP48 package.

#### **APPLICATIONS**

• GSM 900 MHz, DCS 1800 MHz and PCS 1900 MHz hand-held transceivers.

## **GENERAL DESCRIPTION**

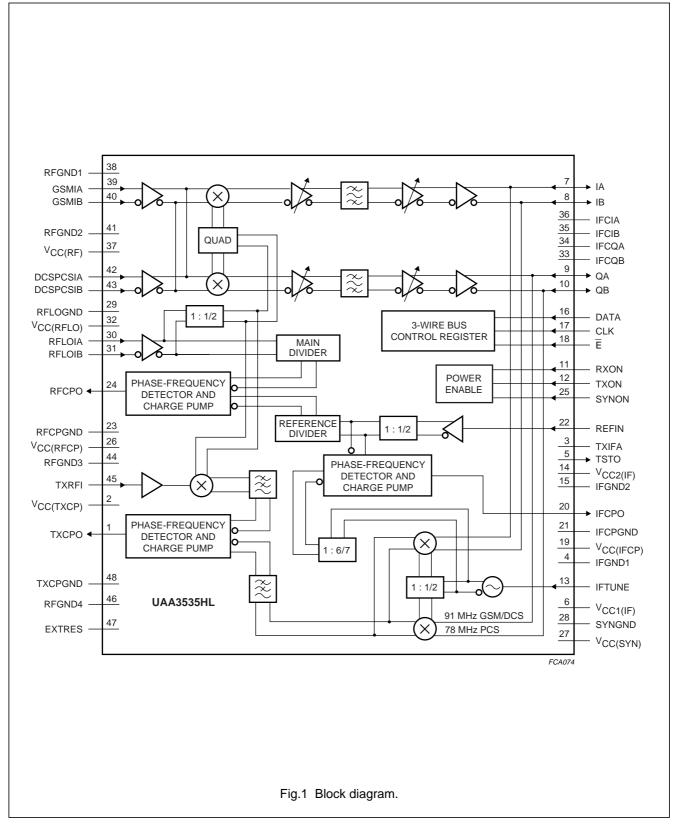

The UAA3535HL is intended for Global Systems for Mobile communication (GSM), Digital Cellular communication Systems (DCS) and Personal Communication Services (PCS). The circuit integrates the receiver and most of the transmitter section of hand-held transceivers for these applications.

The receiver consists of two sections. The first section is the RF receiver front-end, which amplifies the GSM, DCS or PCS aerial signal, then converts the chosen channel down to a low Intermediate Frequency (IF) of 100 kHz, and also provides more than 35 dB image suppression. Some selectivity is provided at this stage by an on-chip low-pass filter and channel selectivity is provided by a high performance integrated band-pass filter. The second section is the IF section, which further amplifies the chosen channel and performs gain control to adjust the output level to the desired value. The IF gain can be varied over more than 64 dB gain range.

The transmitter also consists of two sections. The first is a high precision I/Q modulator which converts the baseband modulation up to the transmit IF. The second is a modulation loop architecture which converts the signal to RF.

The Local Oscillator (LO) signals are provided by an on-chip Voltage Controlled Oscillator (VCO) for operation of the IF section and are provided externally for operation of the RF section. The frequencies of the RF and IF VCOs are set by internal PLL circuits, which are programmable via a 3-wire serial bus. Comparison frequencies are 200 kHz (100 kHz step programmability) and 13 MHz for the RF and IF PLL respectively, and are derived from a 13 MHz reference signal which has to be supplied externally. The quadrature-phase RF LO signals required for I/Q mixers in reception are generated internally. The quadrature LO signals required for operation of the I/Q modulator are generated inside the IF VCO.

The circuit can be powered-up into one of three different modes: RX, TX or SYN mode, depending on the logic state of pins RXON, TXON and SYNON, respectively. It is also possible to set the IC in one of these modes by software, using the 3-wire bus serial programming. In RX (TX) mode, all sections required for receive (transmit) are turned on. The SYN mode is used to power-up the synthesizers prior to the RX or TX mode. In the SYN mode, some internal LO buffers are also powered-up in such a way that VCO pulling is minimized when switching on the receiver or the transmitter. Additional band selection is done using the 3-wire bus serial programming, allowing the required enabling of the Low Noise Amplifiers (LNAs) and charge pumps current programming.

#### **ORDERING INFORMATION**

| TYPE      | PACKAGE |                                                                                  |          |

|-----------|---------|----------------------------------------------------------------------------------|----------|

| NUMBER    | NAME    | DESCRIPTION                                                                      | VERSION  |

| UAA3535HL | LQFP48  | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm | SOT313-2 |

# UAA3535HL

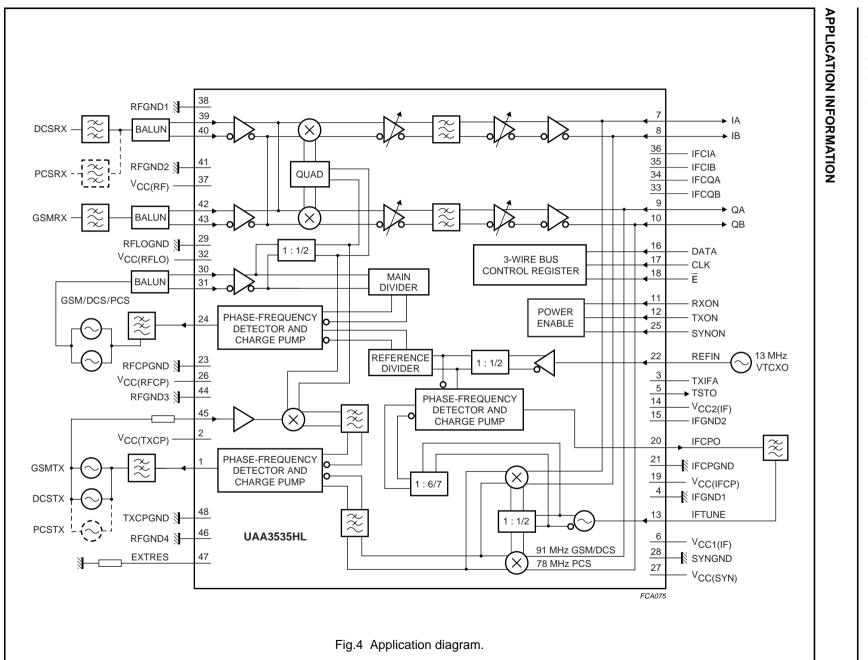

# **BLOCK DIAGRAM**

UAA3535HL

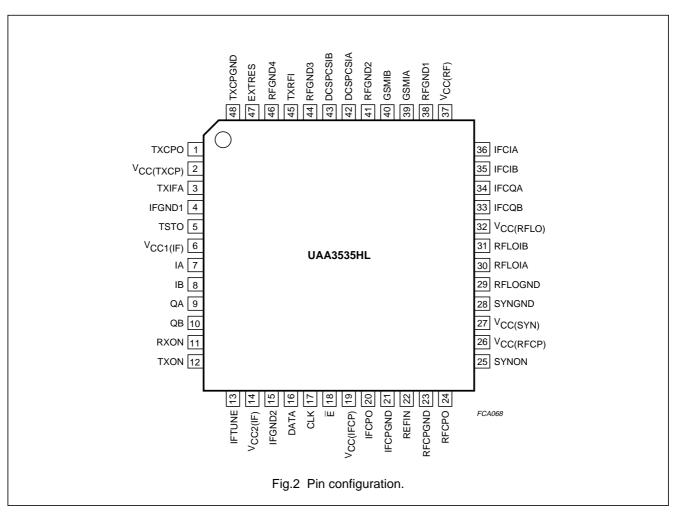

# PINNING

| SYMBOL                | PIN | DESCRIPTION                                         |

|-----------------------|-----|-----------------------------------------------------|

| ТХСРО                 | 1   | transmit modulation loop GSM charge pump output     |

| V <sub>CC(TXCP)</sub> | 2   | transmit modulation loop charge pump supply voltage |

| TXIFA                 | 3   | transmit IF test pin                                |

| IFGND1                | 4   | IF ground 1                                         |

| TSTO                  | 5   | test mode output                                    |

| V <sub>CC1(IF)</sub>  | 6   | IF supply voltage 1                                 |

| IA                    | 7   | I path A baseband input/output                      |

| IB                    | 8   | I path B baseband input/output                      |

| QA                    | 9   | Q path A baseband input/output                      |

| QB                    | 10  | Q path B baseband input/output                      |

| RXON                  | 11  | RX mode control input                               |

| TXON                  | 12  | TX mode control input                               |

| IFTUNE                | 13  | transmit IF VCO tune input                          |

| V <sub>CC2(IF)</sub>  | 14  | IF supply voltage 2                                 |

| IFGND2                | 15  | IF ground 2                                         |

| DATA                  | 16  | 3-wire bus data input                               |

| CLK                   | 17  | 3-wire bus clock input                              |

| Ē                     | 18  | 3-wire bus enable control input (active LOW)        |

| V <sub>CC(IFCP)</sub> | 19  | transmit IF charge pump supply voltage              |

| IFCPO                 | 20  | transmit IF charge pump output                      |

| IFCPGND               | 21  | transmit IF charge pump ground                      |

| REFIN                 | 22  | synthesizers reference input                        |

| RFCPGND               | 23  | RF charge pump ground                               |

| RFCPO                 | 24  | RF charge pump output                               |

| SYNON                 | 25  | SYN mode control input                              |

| SYMBOL                | PIN | DESCRIPTION                     |

|-----------------------|-----|---------------------------------|

| V <sub>CC(RFCP)</sub> | 26  | RF charge pump supply voltage   |

| V <sub>CC(SYN)</sub>  | 27  | synthesizers supply voltage     |

| SYNGND                | 28  | synthesizers ground             |

| RFLOGND               | 29  | RF LO ground                    |

| RFLOIA                | 30  | RF LO input A                   |

| RFLOIB                | 31  | RF LO input B                   |

| V <sub>CC(RFLO)</sub> | 32  | RF LO supply voltage            |

| IFCQB                 | 33  | RX IF Q test pin B              |

| IFCQA                 | 34  | RX IF Q test pin A              |

| IFCIB                 | 35  | RX IF I test pin B              |

| IFCIA                 | 36  | RX IF I test pin A              |

| V <sub>CC(RF)</sub>   | 37  | RF front-end and transmit       |

|                       |     | modulation loop supply voltage  |

| RFGND1                | 38  | RF front-end and transmit       |

|                       |     | modulation loop ground 1        |

| GSMIA                 | 39  | receiver GSM RF input A         |

| GSMIB                 | 40  | receiver GSM RF input B         |

| RFGND2                | 41  | RF front-end and transmit       |

|                       |     | modulation loop ground 2        |

| DCSPCSIA              | 42  | receiver DCS/PCS RF input A     |

| DCSPCSIB              | 43  | receiver DCS/PCS RF input B     |

| RFGND3                | 44  | RF front-end and transmit       |

|                       |     | modulation loop ground 3        |

| TXRFI                 | 45  | input from RF transmit VCOs     |

| RFGND4                | 46  | RF front-end and transmit       |

|                       |     | modulation loop ground 4        |

| EXTRES                | 47  | reference resistor for transmit |

|                       |     | modulation loop                 |

| TXCPGND               | 48  | transmit modulation loop charge |

|                       |     | pump ground                     |

# UAA3535HL

# FUNCTIONAL DESCRIPTION

## **RF** receiver

The receiver front-end converts the aerial RF signal from EGSM (Extended GSM; 925 to 960 MHz), DCS (1805 to 1880 MHz) or PCS (1930 to 1990 MHz) bands down to an IF signal of 100 kHz. The first stages are symmetrical LNAs that are matched to 50  $\Omega$  using external baluns. The LNAs are followed by an I/Q down-mixer. The I/Q down-mixer consists of two mixers in parallel but driven by quadrature out of phase LO signals. The In-phase (I) and Quadrature- phase (Q) IF signals are then low-pass filtered to provide protection from high frequency offset interferers. The IF I and Q signals are then fed into the channel filter.

# Channel filter and AGC

The front-end IF I and Q outputs are first applied to an amplifier circuit with provision for three 8 dB gain step adjustment possibilities and then to an integrated band-pass channel filter. The filter is a fifth-order band-pass filter centred around 100 with 220 kHz bandwidth. After filtering the IF I and Q signals are further amplified with provision for eleven 4 dB gain steps and DC offset compensation.

## I/Q modulator

I and Q baseband signals are applied to the I/Q modulator where the modulation spectrum is shifted up to the transmit IF frequency. For low harmonic distortion, low carrier leakage and high image rejection, the phase error must be kept as small as possible. The IF output of the modulator is fed to an integrated low-pass filter where unwanted spurious signals are suppressed, prior to being fed to the phase detector.

# UAA3535HL

#### **Transmit modulation loop**

The analog transmit modulation loop consists of an on-chip offset mixer, a phase-frequency detector, an off-chip loop filter and a transmit VCO. The analog PLL copies the modulation to the off-chip transmit VCO and acts as a tracking filter. A PLL of at least third-order is required to meet noise requirements at 20 MHz offset from the carrier. The PLL bandwidth must be greater than 600 kHz in order to keep a low dynamic phase error and to minimize the acquisition time.

#### **RF and IF LO sections**

The RF LO input covering the 1788 to 2002 MHz bandwidth is connected to an external RF VCO module. The RF LO section includes the LO buffering for the RF PLL, a divider-by-2 or 1 for GSM and DCS/PCS respectively which drives a quadrature generation network for use in the RX I/Q down-mixer or the transmit modulation loop offset mixer. The IF LO section consists of a fully integrated IF VCO which internally provides the I/Q modulator with the necessary quadrature signals.

#### Dual PLL

A high performance dual PLL is included on-chip which enables the frequencies of the RF VCO to be synthesized off-chip and that of the IF VCO on-chip. Very low close-in phase noise is achieved which allows the PLL loop bandwidth to be widened to achieve a shorter settling time. The charge pump circuit has very low leakage current, in the nA range, so that the spurious signals are hardly detectable. The 'main' path consists of a programmable divider chain that divides the RF and IF LO signals down to frequencies of 200 kHz (100 kHz step programmability) and 13 MHz respectively. Their phase is then compared in a digital Phase-Frequency Detector (PFD) with that of a reference signal derived from an external 13 or 26 MHz clock signal. The phase error information is fed back to the VCO via the charge pump circuit that 'sinks' into or 'sources' current from the loop filter capacitor, thereby changing the VCO frequency so that the loop becomes 'phase locked'.

## **Operating modes**

BASIC OPERATING MODES

The circuit can be powered-up into different operating modes depending on the voltage level applied at pins RXON, TXON and SYNON (hardware control). This defines the three main modes; RX, TX and SYN. Table 1 describes the different operating modes as defined by hardware control.

The operation mode status depends on the control bits SYNON, RXON and TXON (see Table 1).

When the receiver is on, it is possible to switch-off the low noise amplifier to perform DC offset compensation in the receiver (see Section "LNA power control").

When in TX mode, it is possible to enable the IF synthesizer and VCO independently from the rest of the TX section via bit TXIFON via the control bus.

| MODE | CONTROL PIN LEVEL |      | POWER STATUS |             |          |             |

|------|-------------------|------|--------------|-------------|----------|-------------|

| MODE | SYNON             | RXON | TXON         | SYNTHESIZER | RECEIVER | TRANSMITTER |

| SYN  | HIGH              | LOW  | LOW          | on          | off      | off         |

| RX   | HIGH              | HIGH | LOW          | on          | on       | off         |

| ТХ   | HIGH              | LOW  | HIGH         | on          | off      | on          |

| Idle | LOW               | LOW  | LOW          | off         | off      | off         |

| Table 1 | Basic operating mode control |

|---------|------------------------------|

|---------|------------------------------|

UAA3535HL

IF SYNTHESIZER AND VCO CONTROL

The IF synthesizer is only necessary in transmit mode. The TX IF VCO and synthesizer section can be powered-up with the control bit TXIFON; see Table 2. If TXIFON is not used, the IF VCO and synthesizer section will be enabled with the signal TXON.

| Table 2 | IF synthesizer and VCO power control |

|---------|--------------------------------------|

|         |                                      |

| BIT TXIFON | IF SYNTHESIZER AND<br>VCO MODE |

|------------|--------------------------------|

| 0          | off                            |

| 1          | on                             |

LNA POWER CONTROL

When the receiver is on, it is possible to switch-off the low noise amplifier separately. Separate control of the low noise amplifier is accomplished by the control bit LNA; see Table 3.

| Table 3 | LNA | power | control |

|---------|-----|-------|---------|

|---------|-----|-------|---------|

| BIT LNA | LNA MODE |

|---------|----------|

| 0       | off      |

| 1       | on       |

BAND SELECTION CONTROL

The receiver includes two RF front-end and RF LO sections; one for GSM where the RF LO is divided-by-2 and fed to the 925 to 960 MHz front-end, and the other one for DCS and/or PCS where the RF LO is not divided and fed to the 1805 to 1990 MHz front-end. The selection of these 2 modes is accomplished by the control bit BND; see Table 4.

| Table 4 Band selection cor | ntrol |

|----------------------------|-------|

|----------------------------|-------|

| BIT BND | BAND MODE      |

|---------|----------------|

| 0       | GSM            |

| 1       | DCS and/or PCS |

SIDEBAND SELECTION CONTROL

The receiver includes an image rejection front-end which allows the use of a RF LO 100 kHz below the RF input frequency (infradyne) or 100 kHz above the RF input frequency (supradyne). Between these two states the proper image should be selected for rejection. The selection of these 2 modes is accomplished by the control bit SBD; see Table 5.

| Table 5 | Sideband selection control |

|---------|----------------------------|

|---------|----------------------------|

| BIT SBD SIDEBAND MODE |           |  |  |  |  |  |

|-----------------------|-----------|--|--|--|--|--|

| 0                     | supradyne |  |  |  |  |  |

| 1                     | infradyne |  |  |  |  |  |

TX CHARGE PUMP CURRENT CONTROL

The transmit modulation loop includes a transmit charge pump where sink and source currents are determined by an external resistor. When determined, this nominal current can be divided-by-1 or 2 to cope with different transmit VCO gains. The selection of these 2 modes is accomplished by the control bit TXI; see Table 6.

#### Table 6 TX charge pump current control

| BIT TXI | TX CHARGE PUMP CURRENT MODE  |

|---------|------------------------------|

| 0       | nominal current              |

| 1       | nominal current divided-by-2 |

REFERENCE DIVIDER CONTROL

The reference divider can be programmed to divide the external reference frequency by 65 or 130. The selection of these 2 modes is accomplished by the control bit REFDIV; see Table 7.

| Table 7 | Reference | divider | control |

|---------|-----------|---------|---------|

|         |           |         |         |

| BIT REFDIV | REFERENCE DIVIDER MODE |

|------------|------------------------|

| 0          | divide-by-65           |

| 1          | divide-by-130          |

UAA3535HL

IF DIVIDER CONTROL

The IF divider can be programmed to divide the integrated IF VCO frequency by 1 or 2. The selection of these 2 modes is accomplished by the control bit IFDIV; see Table 8.

## Table 8 IF divider control

| BIT IFDIV | IF DIVIDER MODE             |

|-----------|-----------------------------|

| 0         | $IF = f_{VCO}$              |

| 1         | $IF = f_{VCO}$ divided by 2 |

TXIF FILTER CONTROL

The transmit section integrates two switchable low-pass filters, one for a 45.5 MHz IF and the other one for 91 MHz IF. The selection of these 2 modes is accomplished by the control bit FILT; see Table 9.

#### Table 9 TXIF filter control

| BIT FILT | TXIF FILTER MODE |

|----------|------------------|

| 0        | IF 45.5 MHz      |

| 1        | IF 91 MHz        |

IF SYNTHESIZER DIVIDER CONTROL

The IF synthesizer divider can be programmed to divide the semi-integrated IF VCO frequency by 6 or 7. The selection of these 2 modes is accomplished by the control bit IFO; see Table 10.

## Table 10 IF synthesizer divider control

| BIT IFO | IF SYNTHESIZER<br>DIVIDER MODE |

|---------|--------------------------------|

| 0       | divide-by-6                    |

| 1       | divide-by-7                    |

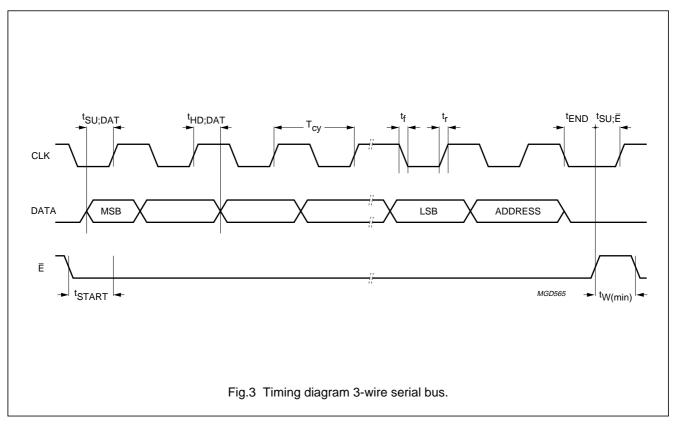

# Programming

#### SERIAL PROGRAMMING BUS

A simple 3-wire unidirectional serial bus is used to program the circuit. The 3 lines are DATA, CLK and  $\overline{E}$  (enable). The data sent to the device is loaded in bursts framed by  $\overline{E}$ . Programming clock edges are ignored until  $\overline{E}$  goes active LOW. The programmed information is loaded into the addressed latch when  $\overline{E}$  returns inactive HIGH. This is allowed when CLK is in either state without causing any consequences to the register data. Only the last 17 bits serially clocked into the device are retained within the programming register. Additional leading bits are ignored, and no check is made on the number of clock pulses. The fully static CMOS design uses virtually no current when the bus is inactive. It can always capture new programming data even during power-down of both synthesizers.

#### DATA FORMAT

Data is entered with the most significant bit first. The leading bits make up the data field, while the trailing 4 bits are an address field. The address bits are decoded on the rising edge of  $\overline{E}$ . This produces an internal load pulse to store the data in the addressed latch. To ensure that data is correctly loaded on first power-up,  $\overline{E}$  should be held LOW and only taken High after having programmed an appropriate register. To avoid erroneous divider ratios, the pulse is inhibited during the period when data is read by the frequency dividers. This condition is guaranteed by respecting a minimum  $\overline{E}$  pulse width after data transfer.

The allocation of the register bits is given in Table 11.

## **REGISTER PRESET CONDITIONS**

The UAA3535HL programming registers have a preset state. The preset values can be found in Table 12. Conditions for guaranteed preset values at power-on are as follows:

- DATA, CLOCK,  $\overline{\mathsf{E}},$  SYNON, RXON and TXON must be at 0 V

- Preset value is guaranteed 2 ms after  $V_{CC(SYN)}$  rises to 90% of 2.6 V

- E should stay at 0 V up to the end of the first programming word.

Table 11

Register bit allocation; notes 1 and 2 and 3

|           | REGISTER ALLOCATION |           |           |            |            |           |           |          |           |           |          |          |            |           |          |          |            |    |      |    |

|-----------|---------------------|-----------|-----------|------------|------------|-----------|-----------|----------|-----------|-----------|----------|----------|------------|-----------|----------|----------|------------|----|------|----|

|           | DATA FIELD          |           |           |            |            |           |           |          |           |           |          |          |            |           |          | A        | DDF<br>FIE | -  | S    |    |

| BIT<br>16 | BIT<br>15           | BIT<br>14 | BIT<br>13 | BIT<br>12  | BIT<br>11  | BIT<br>10 | BIT<br>9  | BIT<br>8 | BIT<br>7  | BIT<br>6  | BIT<br>5 | BIT<br>4 | BIT<br>3   | BIT<br>2  | BIT<br>1 | BIT<br>0 | LA         | ST | 4 Bľ | TS |

| Х         | Х                   | RF<br>14  | RF<br>13  | RF<br>12   | RF<br>11   | RF<br>10  | RF<br>9   | RF<br>8  | RF<br>7   | RF<br>6   | RF<br>5  | RF<br>4  | RF<br>3    | RF<br>2   | RF<br>1  | RF<br>0  | 0          | 0  | 1    | 1  |

| Х         | Х                   | Х         | Х         | Х          | 0          | 0         | 0         | 0        | 0         | LNA       | G5       | G4       | G3         | G2        | G1       | G0       | 0          | 0  | 1    | 0  |

| Х         | Х                   | X         | 0         | FILT       | REF<br>DIV | IFO       | IF<br>DIV | TXI      | SBD       | BND       | 1        | 1        | TXIF<br>ON | SYN<br>ON | RX<br>ON | TX<br>ON | 0          | 0  | 0    | 1  |

|           |                     | •         | fc        | or test pu | urpose c   | nly; bit  | usage to  | be def   | ined; thi | s is a fo | rbidden  | addres   | S          |           |          |          | 0          | 0  | 0    | 0  |

#### Notes

ဖ

2000 Feb 17

1. The 15-bit RF divider is programmable through the 15 bits RF0 to RF14, in steps of 100 kHz.

2. X = don't care.

3. The 6-bit AGC attenuator is programmable through the 6 bits G0 to G5 in 17 steps of 4 dB (see Table 13).

Table 12 Preset values; note 1

|           | REGISTER ALLOCATION                                                         |           |           |           |           |           |          |          |          |          |          |          |          |          |          |          |    |             |   |   |

|-----------|-----------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----|-------------|---|---|

|           | DATA FIELD                                                                  |           |           |           |           |           |          |          |          |          |          |          |          |          |          | A        |    | RES<br>ELD  | S |   |

| BIT<br>16 | BIT<br>15                                                                   | BIT<br>14 | BIT<br>13 | BIT<br>12 | BIT<br>11 | BIT<br>10 | BIT<br>9 | BIT<br>8 | BIT<br>7 | BIT<br>6 | BIT<br>5 | BIT<br>4 | BIT<br>3 | BIT<br>2 | BIT<br>1 | BIT<br>0 | LA | LAST 4 BITS |   |   |

| Х         | Х                                                                           | 1         | 0         | 0         | 1         | 0         | 1        | 0        | 0        | 0        | 0        | 0        | 0        | 1        | 1        | 0        | 0  | 0           | 1 | 1 |

| Х         | Х                                                                           | Х         | Х         | Х         | 0         | 0         | 0        | 0        | 0        | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 0  | 0           | 1 | 0 |

| Х         | Х                                                                           | Х         | 0         | 0         | 0         | 1         | 1        | 0        | 1        | 0        | 1        | 1        | 0        | 0        | 0        | 0        | 0  | 0           | 0 | 1 |

|           | for test purpose only; bit usage to be defined; this is a forbidden address |           |           |           |           |           |          |          |          |          |          | 0        | 0        | 0        | 0        |          |    |             |   |   |

# Note

1. X = don't care.

Low power GSM/DCS/PCS multi-band transceiver

# UAA3535HL

| <b>G5</b> <sup>(2)</sup> | <b>G4</b> <sup>(2)</sup> | G3 | G2 | G1 | G0 | ATTENUATION (dB) <sup>(3)</sup> |

|--------------------------|--------------------------|----|----|----|----|---------------------------------|

| 1                        | 1                        | 1  | 1  | 1  | 1  | 0                               |

| 1                        | 1                        | 1  | 1  | 1  | 0  | 4                               |

| 1                        | 0                        | 1  | 1  | 1  | 1  | 8                               |

| 1                        | 0                        | 1  | 1  | 1  | 0  | 12                              |

| 0                        | 1                        | 1  | 1  | 1  | 1  | 16                              |

| 0                        | 1                        | 1  | 1  | 1  | 0  | 20                              |

| 0                        | 1                        | 1  | 1  | 0  | 1  | 24                              |

| 0                        | 1                        | 1  | 1  | 0  | 0  | 28                              |

| 0                        | 1                        | 0  | 1  | 1  | 1  | 32                              |

| 0                        | 1                        | 0  | 1  | 1  | 0  | 36                              |

| 0                        | 0                        | 0  | 1  | 1  | 1  | 40                              |

| 0                        | 0                        | 0  | 1  | 1  | 0  | 44                              |

| 0                        | 0                        | 0  | 1  | 0  | 1  | 48                              |

| 0                        | 0                        | 0  | 1  | 0  | 0  | 52                              |

| 0                        | 0                        | 0  | 0  | 1  | 1  | 56                              |

| 0                        | 0                        | 0  | 0  | 1  | 0  | 60                              |

| 0                        | 0                        | 0  | 0  | 0  | 1  | 64                              |

| 0                        | 0                        | 0  | 0  | 0  | 0  | 68                              |

#### Table 13 AGC gain look-up table; note 1

**Philips Semiconductors**

## Notes

1. Codes not included in the table are forbidden.

2. Steps at the input of the band-pass filter.

3. The figure represents the total attenuation in the receive path, with respect to the maximum gain.

# UAA3535HL

## LIMITING VALUES

| SYMBOL                                           | DESCRIPTION                               | MIN. | MAX.  | UNIT |

|--------------------------------------------------|-------------------------------------------|------|-------|------|

| V <sub>CC</sub>                                  | supply voltage                            | -0.3 | +3.6  | V    |

| V <sub>CC(TXCP)</sub> ;<br>V <sub>CC(RFCP)</sub> | supply voltage for RX and TX charge pumps | -0.3 | +4.25 | V    |

| P <sub>max</sub>                                 | maximum power dissipation                 | -    | 1     | W    |

| T <sub>amb</sub>                                 | ambient temperature                       | -30  | +70   | °C   |

| T <sub>stg</sub>                                 | storage temperature                       | -40  | +150  | °C   |

# THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                | VALUE | UNIT |

|----------------------|------------------------------------------|-------|------|

| R <sub>th(j-c)</sub> | thermal resistance from junction to case | 65    | K/W  |

## DC CHARACTERISTICS

$V_{CC}$  =  $V_{CC(TXCP)}$  =  $V_{CC(RFCP)}$  = 2.6 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL               | PARAMETER                                                      | CONDITIONS                                                      | MIN. | TYP. | MAX. | UNIT |

|----------------------|----------------------------------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| I <sub>CC</sub>      | supply current                                                 | normal mode; total power-down;<br>note 1                        | -    | 10   | 50   | μΑ   |

|                      |                                                                | preset mode; total power-down;<br>note 2                        | -    | 100  | 200  | μΑ   |

|                      |                                                                | RX and SYN mode                                                 | -    | 51.5 | 60   | mA   |

|                      |                                                                | TX, TXIF and SYN mode                                           | -    | 54   | 66   | mA   |

|                      |                                                                | SYN mode                                                        | -    | 17   | 20   | mA   |

|                      |                                                                | TXIF and SYN mode                                               | _    | 29   | 37   | mA   |

| V <sub>CC(RF)</sub>  | RF front-end and transmit<br>modulation loop supply<br>voltage |                                                                 | 2.4  | -    | 3.3  | V    |

| I <sub>CC(RF)</sub>  | RF front-end and transmit modulation loop supply               | RX mode; one LNA and quadrature mixer active                    | -    | 17   | -    | mA   |

|                      | current                                                        | RX mode; one LNA active                                         | -    | 6    | -    | mA   |

|                      |                                                                | TX mode; transmit modulation<br>loop active without charge pump | _    | 6    | -    | mA   |

| V <sub>CC1(IF)</sub> | IF supply voltage 1                                            |                                                                 | 2.4  | -    | 3.3  | V    |

| I <sub>CC1(IF)</sub> | IF supply current 1                                            | RX mode; I/Q low IF band-pass filter active                     | _    | 7    | -    | mA   |

|                      |                                                                | TX mode; I/Q modulator active                                   | -    | 9    | -    | mA   |

| V <sub>CC2(IF)</sub> | IF supply voltage 2                                            |                                                                 | 2.4  | -    | 3.3  | V    |

| I <sub>CC2(IF)</sub> | IF supply current 2                                            | RX mode; I/Q AGC active                                         | -    | 4    | -    | mA   |

|                      |                                                                | TXIF mode; TX IF VCO active                                     | -    | 9    | -    | mA   |

# UAA3535HL

| SYMBOL                | PARAMETER                                              | CONDITIONS                                                                             | MIN. | TYP. | MAX. | UNIT |

|-----------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>CC(RFLO)</sub> | RF LO supply voltage                                   |                                                                                        | 2.4  | _    | 3.3  | V    |

| I <sub>CC(RFLO)</sub> | RF LO supply current                                   | RX and SYN mode; RF LO buffer and divider section active                               | -    | 10   | -    | mA   |

|                       |                                                        | TX and SYN mode; RF LO buffer and divider section active                               | -    | 10   | -    | mA   |

|                       |                                                        | SYN mode; RF LO buffer active                                                          | -    | 6    | -    | mA   |

| V <sub>CC(SYN)</sub>  | synthesizers supply voltage                            |                                                                                        | 2.4  | -    | 3.3  | V    |

| I <sub>CC(SYN)</sub>  | synthesizers supply current                            | SYN mode; RF synthesizer active                                                        | -    | 9.5  | -    | mA   |

|                       |                                                        | TXIF mode; IF synthesizer active                                                       | -    | 0.5  | -    | mA   |

| V <sub>CC(IFCP)</sub> | transmit IF charge pump<br>supply voltage              |                                                                                        | 2.4  | -    | 3.3  | V    |

| I <sub>CC(IFCP)</sub> | transmit IF charge pump<br>supply current              | TXIF mode; IF LO charge pump active; in lock                                           | -    | 1.5  | -    | mA   |

| V <sub>CC(TXCP)</sub> | transmit modulation loop<br>charge pump supply voltage |                                                                                        | 2.4  | -    | 4.25 | V    |

| I <sub>CC(TXCP)</sub> | transmit modulation loop<br>charge pump supply current | TX mode; TX RF charge pump<br>active; in lock; external<br>resistance is 1800 $\Omega$ | -    | 1.0  | -    | mA   |

| V <sub>CC(RFCP)</sub> | RF charge pump supply voltage                          |                                                                                        | 2.4  | -    | 4.25 | V    |

| I <sub>CC(RFCP)</sub> | RF charge pump supply current                          | SYN mode; RF LO charge pump active; in lock                                            | -    | 4.5  | -    | mA   |

| Baseband se           | ection: pins IA, IB, QA and QB                         |                                                                                        |      | •    | •    | •    |

| V <sub>I(CM)</sub>    | common mode input-output voltage I                     | $V_{I} = \frac{V_{IA} + V_{IB}}{2}$                                                    | 1.15 | 1.25 | 1.35 | V    |

| V <sub>Q(CM)</sub>    | common mode input-output voltage Q                     | $V_{Q} = \frac{V_{QA} + V_{QB}}{2}$                                                    | 1.15 | 1.25 | 1.35 | V    |

| Logic input l         | evels: pins DATA, CLK, Ē, TXC                          | N, RXON and SYNON                                                                      |      |      | 1    |      |

| V <sub>IH</sub>       | HIGH-level input voltage                               |                                                                                        | 0.9  | _    | _    | V    |

| VIL                   | LOW-level input voltage                                |                                                                                        | _    | _    | 0.3  | V    |

## Notes

1.  $V_{CC(TXCP)} = V_{CC(RFCP)} = 4.2 V$ ; pins TXON, RXON and SYNON are HIGH impedance; pins DATA, CLK and  $\overline{E}$  are HIGH impedance.

2.  $V_{CC(TXCP)} = V_{CC(RFCP)} = 4.2 V$ ; pins TXON, RXON and SYNON are LOW; pins DATA, CLK and  $\overline{E}$  are HIGH.

# UAA3535HL

# AC CHARACTERISTICS

$V_{CC}$  =  $V_{CC(CP)}$  = 2.6 V;  $T_{amb}$  = –30 to +70  $^{\circ}C;$  unless otherwise specified.

| SYMBOL                  | PARAMETER                                         | CONDITIONS                                                             | MIN.      | TYP.       | MAX.         | UNIT    |

|-------------------------|---------------------------------------------------|------------------------------------------------------------------------|-----------|------------|--------------|---------|

| RF receiver networks to | section; measured in a 50 $\Omega$ in 50 $\Omega$ | npedance system, includin                                              | ig extern | al input k | baluns and m | atching |

| PINS: GSMIA             | AND GSMIB                                         |                                                                        |           |            |              |         |

| f <sub>i(RF)</sub>      | RF input frequency                                |                                                                        | 925       | _          | 960          | MHz     |

| R <sub>i(dif)</sub>     | differential input resistance                     | parallel RC input model                                                | _         | 75         | _            | Ω       |

| C <sub>i(dif)</sub>     | differential input capacitance                    | parallel RC input model                                                | -         | 1.5        | -            | pF      |

| F                       | noise figure                                      | for R <sub>i</sub> ; maximum AGC;<br>notes 1 and 2                     | -         | 3.5        | 4            | dB      |

| $\alpha_{\text{off}}$   | LNA off-state attenuation                         | bit LNA = 0; note 1                                                    | _         | 45         | -            | dB      |

| Poff                    | LNA off-state power handling                      | bit LNA = 0; notes 1 and 3                                             | 3         | _          | -            | dBm     |

| DES3 <sub>i</sub>       | input referred 3 dB desensitization               | $\Delta f = 3 \text{ MHz}; \text{ T}_{amb} = 25 \text{ °C};$<br>note 1 | -25       | -          | -            | dBm     |

| PINS: DCSPC             | SIA AND DCSPCSIB                                  |                                                                        |           |            |              |         |

| f <sub>i(RF)</sub>      | RF input frequency                                |                                                                        | 1805      | _          | 1990         | MHz     |

| R <sub>i(dif)</sub>     | differential input resistance                     | parallel RC input model                                                | _         | 120        | _            | Ω       |

| C <sub>i(dif)</sub>     | differential input capacitance                    | parallel RC input model                                                | -         | 1.0        | -            | pF      |

| F                       | noise figure                                      | for R <sub>i</sub> ; maximum AGC;<br>notes 1 and 2                     | -         | 4          | 4.5          | dB      |

| $\alpha_{\text{off}}$   | LNA off-state attenuation                         | bit LNA = 0; note 1                                                    | _         | 45         | -            | dB      |

| P <sub>off</sub>        | LNA off-state power handling                      | bit LNA = 0; notes 1 and 3                                             | 6         | _          | -            | dBm     |

| DES3 <sub>i</sub>       | input referred 3 dB desensitization               | $\Delta f = 3 \text{ MHz}; \text{ T}_{amb} = 25 \text{ °C};$<br>note 1 | -28       | -          | -            | dBm     |

| PINS: GSMIA             | , GSMIB, DCSPCSIA AND DCSF                        | PCSIB                                                                  | •         | •          | -            | •       |

| S <sub>11</sub>         | input reflection coefficient                      | note 2                                                                 | _         | -15        | -10          | dB      |

| SPUR <sub>P(RFin)</sub> | power level of spurious                           | 900 to 1000 MHz band                                                   | _         | _          | -57          | dBm     |

| ~ /                     | signals at RF input                               | 1800 to 2000 MHz band                                                  | -         | _          | -47          | dBm     |

|                         |                                                   | out of preceding bands                                                 | _         | _          | -45          | dBm     |

| CP1                     | 1 dB input compression point                      | minimum AGC;<br>T <sub>amb</sub> = 25 °C; note 1                       | -25       | -          | -            | dBm     |

| IP3 <sub>i</sub>        | input referred third-order<br>intercept           | maximum AGC;<br>T <sub>amb</sub> = 25 °C; note 1                       | -18       | -          | -            | dBm     |

| IP2 <sub>i</sub>        | input referred second-order intercept             | maximum AGC; note 4                                                    | -         | 30         | -            | dBm     |

| DES3 <sub>i</sub>       | input referred 3 dB<br>desensitization            | $\Delta f = 3 \text{ MHz}; \text{ T}_{amb} = 25 \text{ °C};$<br>note 1 | -23       | -          | -            | dBm     |

| IR                      | image rejection                                   | f <sub>IF</sub> = 200 kHz;<br>T <sub>amb</sub> = 25 °C; note 1         | 35        | 38         | -            | dB      |

| $\Delta G_{v(RF)}$      | gain mismatch GSM and DCS paths                   | note 5                                                                 | -         | -          | 2            | dB      |

| SYMBOL                                                                                          | PARAMETER                                                                                                      | CONDITIONS                                                                                                                                               | MIN.                  | TYP.         | MAX.                           | UNIT                |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------|--------------------------------|---------------------|

| PINS IA, IB, O                                                                                  | QA AND QB (RX MODE)                                                                                            |                                                                                                                                                          |                       |              | -                              |                     |

| G <sub>v(min)</sub>                                                                             | minimum voltage conversion gain                                                                                | gain set to minimum;<br>notes 1 and 5                                                                                                                    | 19                    | 25           | 31                             | dB                  |

| G <sub>v(max)</sub>                                                                             | maximum voltage conversion gain                                                                                | gain set to maximum;<br>notes 1 and 5                                                                                                                    | 89                    | 93           | 97                             | dB                  |

| G <sub>v(step)</sub>                                                                            | voltage conversion gain step                                                                                   | note 5                                                                                                                                                   | -                     | 4            | -                              | dB                  |

| $\Delta G_{v(I/Q)}$                                                                             | gain mismatch I and Q paths                                                                                    | note 5                                                                                                                                                   | _                     | _            | 0.5                            | dB                  |

| $\Delta \Phi$                                                                                   | quadrature-phase error<br>I and Q paths                                                                        | peak error                                                                                                                                               | _                     | -            | 5                              | deg                 |

| LE <sub>AGC</sub>                                                                               | gain control linearity                                                                                         | over full gain range; note 2                                                                                                                             | -2                    | _            | +2                             | dB                  |

|                                                                                                 |                                                                                                                | over any 20 dB gain range                                                                                                                                | -0.5                  | -            | +0.5                           | dB                  |

| V <sub>o(peak)</sub>                                                                            | maximum output voltage per pin                                                                                 | 3% T.H.D.; R <sub>L</sub> = 100 kΩ<br>per pin                                                                                                            | 0.75                  | -            | -                              | V                   |

| I <sub>o(peak)</sub>                                                                            | maximum output current per pin                                                                                 |                                                                                                                                                          | 25                    | 50           | -                              | μA                  |

| Voffset                                                                                         | output offset voltage                                                                                          | under static conditions                                                                                                                                  | -300                  | _            | +300                           | mV                  |

| HP <sub>-3dB</sub>                                                                              | -3 dB high-pass corner<br>frequency                                                                            |                                                                                                                                                          | 4                     | 6            | 8                              | kHz                 |

| B <sub>IF(-3dB)</sub>                                                                           | -3 dB IF filter bandwidth                                                                                      | 100 kHz centre frequency                                                                                                                                 | 220                   | _            | 250                            | kHz                 |

| $\Delta t_{d(g)}$                                                                               | group delay variation                                                                                          | 30 kHz < f <sub>o</sub> < 170 kHz                                                                                                                        | _                     | 1.5          | 2                              | μs                  |

| α <sub>5(IF)</sub>                                                                              | IF filter attenuation                                                                                          | $f_o = 100 \text{ kHz} \pm 200 \text{ kHz}$                                                                                                              | 17                    | 31           | -                              | dB                  |

|                                                                                                 | (fifth-order)                                                                                                  | $f_o = 100 \text{ kHz} \pm 400 \text{ kHz}$                                                                                                              | 54                    | 64           | _                              | dB                  |

|                                                                                                 |                                                                                                                | $f_o = 100 \text{ kHz} \pm 600 \text{ kHz}$                                                                                                              | 73                    | 82           | _                              | dB                  |

| Transmit IF                                                                                     | section (initial conditions: V <sub>mc</sub>                                                                   | <sub>od(peak)</sub> = 0.5 V; f <sub>mod</sub> = 67.7 k                                                                                                   | Hz; unle              | ss other     | wise specified                 | )                   |

| PINS IA, IB, (                                                                                  | QA AND QB (TX MODE)                                                                                            |                                                                                                                                                          |                       |              |                                |                     |

| f <sub>mod</sub>                                                                                | modulation frequency                                                                                           | 3 dB low-pass cut-off frequency                                                                                                                          | 1                     | -            | -                              | MHz                 |

| V <sub>mod(peak)</sub>                                                                          | modulation level                                                                                               | single-ended; peak value                                                                                                                                 | _                     | 0.5          | 0.55                           | V                   |

| R <sub>i(D)</sub>                                                                               | dynamic input resistance                                                                                       | single-ended                                                                                                                                             | _                     | 25           | -                              | kΩ                  |

| IF LO oscilla                                                                                   | ator (measured and guarantee                                                                                   | d on demonstration board a                                                                                                                               | at T <sub>amb</sub> = | = 25 °C)     |                                |                     |

|                                                                                                 |                                                                                                                |                                                                                                                                                          | 1                     |              | 0.1                            |                     |

| f <sub>IFLO</sub>                                                                               | range of possible operation                                                                                    | with programming                                                                                                                                         | 78                    | -            | 91                             | MHz                 |

|                                                                                                 | range of possible operation<br>VCO gain                                                                        | with programming $V_{tune}$ from 0.6 V to $V_{CC} - 0.6$ V                                                                                               | 78                    | 30           | 91                             |                     |

| K <sub>VCO</sub>                                                                                | - · · ·                                                                                                        | V <sub>tune</sub> from 0.6 V to                                                                                                                          |                       | -<br>30<br>- |                                | MHz<br>MHz/V        |

| f <sub>IFLO</sub><br>K <sub>VCO</sub><br>V <sub>tune</sub><br>Δf <sub>VCC</sub>                 | VCO gain                                                                                                       | $V_{tune}$ from 0.6 V to $V_{CC}$ – 0.6 V                                                                                                                | -                     |              | -                              | MHz/V               |

| K <sub>VCO</sub><br>V <sub>tune</sub>                                                           | VCO gain<br>tuning voltage<br>frequency variation with                                                         | $\begin{array}{c} V_{tune} \text{ from } 0.6 \text{ V to} \\ V_{CC} - 0.6 \text{ V} \\ \hline \\ \text{referenced to } V_{CC(IFCP)} \end{array}$         | -                     | _            | -<br>V <sub>CC</sub> - 0.4     | MHz/V<br>V          |

| K <sub>VCO</sub><br>V <sub>tune</sub><br>Δf <sub>VCC</sub><br>Δf <sub>TRON</sub>                | VCO gain<br>tuning voltage<br>frequency variation with<br>respect to the supply voltage                        | $V_{tune} \text{ from } 0.6 \text{ V to} \\ V_{CC} - 0.6 \text{ V} \\ \hline \text{referenced to } V_{CC(IFCP)} \\ \text{pushing} \\ \hline \end{array}$ | -<br>0.4<br>-         | -            | -<br>V <sub>CC</sub> -0.4<br>1 | MHz/V<br>V<br>MHz/V |

| K <sub>VCO</sub><br>V <sub>tune</sub><br>Δf <sub>VCC</sub><br>Δf <sub>TRON</sub><br>Transmit mo | VCO gain<br>tuning voltage<br>frequency variation with<br>respect to the supply voltage<br>frequency variation | $V_{tune} \text{ from } 0.6 \text{ V to} \\ V_{CC} - 0.6 \text{ V} \\ \hline \text{referenced to } V_{CC(IFCP)} \\ \text{pushing} \\ \hline \end{array}$ | -<br>0.4<br>-         | -            | -<br>V <sub>CC</sub> -0.4<br>1 | MHz/V<br>V<br>MHz/V |

| SYMBOL                  | PARAMETER                                       | CONDITIONS                                                                                                        | MIN. | TYP. | MAX.               | UNIT   |

|-------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|--------------------|--------|

| R <sub>i</sub>          | input resistance                                | single-ended                                                                                                      | _    | 50   | -                  | Ω      |

| Ci                      | input capacitance                               | single-ended                                                                                                      | _    | _    | -                  | pF     |

| Pi                      | input power                                     |                                                                                                                   | -23  | -20  | -17                | dBm    |

| s <sub>11</sub>         | input reflection coefficient                    |                                                                                                                   | _    | -10  | -                  | dB     |

| F                       | noise figure                                    | T <sub>amb</sub> = 25 °C                                                                                          | _    | 10   | -                  | dB     |

| CP1                     | 1 dB input compression point                    | T <sub>amb</sub> = 25 °C                                                                                          | _    | -20  | -                  | dBm    |

| SPUR <sub>P(RFin)</sub> | power level of spurious                         | LO leakage                                                                                                        | _    | -50  | -45                | dBm    |

| . ()                    | signals at RF input                             | other                                                                                                             | _    | _    | -45                | dBm    |

| PHASE DETECT            | FOR; PIN TXCPO                                  | I                                                                                                                 |      |      |                    |        |

| I <sub>CP(max)</sub>    | charge pump maximum sink<br>or source current   | GSM mode; external<br>resistance of $1800 \Omega 1\%$<br>for minimum output<br>current; TXI = 0; note 6           | 1    | 2    | 4                  | mA     |

|                         |                                                 | DCS and PCS mode;<br>external resistance of<br>1800 $\Omega$ 1% for minimum<br>output current; TXI = 1;<br>note 6 | 0.5  | 1    | 2                  | mA     |

| KΦ                      | phase-frequency detector gain                   | for I <sub>CP</sub> = 1 mA                                                                                        | -    | 0.16 | -                  | mA/rad |

| ΔΚΦ                     | phase-frequency detector gain variation         | over output voltage range                                                                                         | -    | -    | 10                 | %      |

| Vo                      | output voltage                                  |                                                                                                                   | 0.4  | _    | $V_{CC(CP)} - 0.4$ | V      |

| R <sub>o</sub>          | output resistance                               | $V_o = \frac{V_{CC(PHD)}}{2}$                                                                                     | -    | 10   | _                  | kΩ     |

| R <sub>o(pd)</sub>      | output resistance power<br>down                 | TX mode disabled                                                                                                  | -    | 1    | -                  | kΩ     |

| LOo                     | local oscillator feedthrough                    | note 7                                                                                                            | _    | -40  | -32                | dBc    |

| IM3 <sub>o</sub>        | third-order products level                      | offset +3 $\times$ 67.7 kHz or<br>-3 $\times$ 67.7 kHz; note 7                                                    | -    | -55  | -50                | dBc    |

| IMo                     | image level                                     | f <sub>IFLO</sub> – 67.7 kHz; note 7                                                                              | _    | -45  | -37                | dBc    |

| $\Phi_{NOISE}$          | phase noise output power density                | $\Delta f = 400 \text{ kHz};$<br>T <sub>amb</sub> = 25 °C; note 7                                                 | -    | -    | –117               | dBc/Hz |

|                         |                                                 | $\Delta f = 1.8 \text{ MHz};$<br>T <sub>amb</sub> = 25 °C; note 7                                                 | -    | -    | -117               | dBc/Hz |

|                         |                                                 | $\Delta f = 20 \text{ MHz}; \text{ T}_{amb} = 25 ^{\circ}\text{C}$                                                | _    | _    | -136               | dBc/Hz |

| SPUR <sub>L(4fm)</sub>  | level of spurious signals at $4 \times f_{mod}$ | f <sub>mod</sub> = 67.7 kHz;<br>notes 7 and 8                                                                     | -    | -    | -50                | dBc    |

| SPUR <sub>L(8fm)</sub>  | level of spurious signals at $8 \times f_{mod}$ | f <sub>mod</sub> = 67.7 kHz; note 7                                                                               | -    | -    | -55                | dBc    |

| RF LO buffer            | ,                                               |                                                                                                                   |      |      |                    |        |

| RF SOURCE CO            | ONNECTED AT PIN RFLOIA AND R                    | FLOIB                                                                                                             |      |      |                    |        |

| f <sub>i(RF)</sub>      | RF input frequency                              |                                                                                                                   | 1788 | _    | 2002               | MHz    |

| SYMBOL                  | PARAMETER                               | CONDITIONS                             | MIN. | TYP. | MAX.           | UNIT   |

|-------------------------|-----------------------------------------|----------------------------------------|------|------|----------------|--------|

| R <sub>i(dif)</sub>     | differential input resistance           | parallel RC input model                | _    | 50   | -              | Ω      |

| C <sub>i(dif)</sub>     | differential input capacitance          | parallel RC input model                | _    | 0.2  | -              | pF     |

| s <sub>11</sub>         | input reflection coefficient            |                                        | -    | -15  | -10            | dB     |

| P <sub>LO</sub>         | power available from the LO source      |                                        | -8   | -5   | -2             | dBm    |

| RF and IF sy            | nthesizers                              |                                        | •    |      |                |        |

| REFERENCE IN            | NPUT; PIN REFIN                         |                                        |      |      |                |        |

| f <sub>ref</sub>        | reference frequency                     | REFDIV = 0                             | _    | 13   | _              | MHz    |

|                         |                                         | REFDIV = 1                             | _    | 26   | -              | MHz    |

| V <sub>i(rms)</sub>     | input voltage level<br>(RMS value)      |                                        | 60   | -    | 220            | mV     |

| R <sub>i</sub>          | input resistance                        | f <sub>ref</sub> = 13 MHz              | -    | 10   | -              | kΩ     |

| RF SYNTHESIZ            | ZER; PIN RFCPO                          |                                        |      |      |                |        |

| f <sub>RFLO</sub>       | synthesizer frequency                   |                                        | 1700 | _    | 2100           | MHz    |

| f <sub>comp(RF)</sub>   | comparison frequency                    |                                        | _    | 200  | -              | kHz    |

| f <sub>comp(leak)</sub> | 200 kHz comparison<br>frequency leakage | with recommended loop filter           | -    | -50  | -              | dBc    |

| f <sub>step(RF)</sub>   | frequency step<br>programmability       | $f_{comp(RF)} = 200 \text{ kHz}$       | -    | 100  | -              | kHz    |

| $\Phi_{noise}$          | close-in phase noise                    | $\Delta f = 2 \text{ kHz}$             | _    | -80  | -76            | dBc/Hz |

| SPUR <sub>P(RF)</sub>   | power level of spurious signals         | f > 400 kHz                            | -    | -    | -70            | dBc    |

| I <sub>CP(nom)</sub>    | nominal charge pump output current      | sink or source                         | 1.7  | 2.0  | 2.3            | mA     |

| KΦ                      | phase-frequency detector gain           | $I_{CP} = 2 \text{ mA}$                | -    | 0.32 | -              | mA/rad |

| $\Delta K \Phi$         | phase-frequency detector gain variation | over V <sub>CP</sub> range             | -    | -    | 10             | %      |

| I <sub>L(CP)</sub>      | charge pump leakage current             | in off state                           | -5   | _    | +5             | nA     |

| V <sub>CP</sub>         | charge pump output voltage              | I <sub>CP</sub> within specified range | 0.4  | _    | $V_{CC} - 0.4$ | V      |

| R <sub>o</sub>          | output resistance                       | SYN mode disabled;<br>power-down       | -    | 1    | -              | kΩ     |

# UAA3535HL

| SYMBOL                    | PARAMETER                               | CONDITIONS                                                  | MIN. | TYP. | MAX.           | UNIT   |

|---------------------------|-----------------------------------------|-------------------------------------------------------------|------|------|----------------|--------|

| IF SYNTHESIZE             | R; PINS IFTUNE AND IFCPO                |                                                             | 1    | -1   |                |        |

| f <sub>IFLO</sub>         | synthesizer frequency                   |                                                             | 70   | _    | 100            | MHz    |

| f <sub>comp(IF)</sub>     | comparison frequency                    |                                                             | _    | 13   | -              | MHz    |

| $\Phi_{\sf noise}$        | close-in phase noise                    | ∆f = 400 kHz                                                | _    | _    | -117           | dBc/Hz |

| SPUR <sub>P(IF)</sub>     | power level of spurious signals         |                                                             | -    | -    | -70            | dBc    |

| I <sub>CP</sub>           | charge pump output current              | sink or source                                              | 0.85 | 1.0  | 1.15           | mA     |

| KΦ                        | phase-frequency detector gain           | for I <sub>CP</sub> = 1 mA                                  | -    | 0.16 | -              | mA/rad |

| $\Delta K \Phi$           | phase-frequency detector gain variation | over V <sub>CP</sub> range                                  | -    | -    | 10             | %      |

| IL                        | charge pump leakage current             | off state                                                   | -5   | _    | +5             | nA     |

| V <sub>CP</sub>           | charge pump output voltage              |                                                             | 0.4  | -    | $V_{CC} - 0.4$ | V      |

| R <sub>o</sub>            | output resistance                       | TXIFON and TXON mode disabled; power-down                   | -    | 1    | -              | kΩ     |

| DIVIDERS RATIO            | DS                                      |                                                             |      | •    |                | L      |

| D/D <sub>RF(main)</sub>   | RF main divider ratio                   | ratio between RFLOI<br>frequency and f <sub>comp(RF)</sub>  | 8940 | -    | 10 010         |        |

| D/D <sub>IF(main)</sub>   | IF main divider ratio                   | ratio between IF VCO<br>frequency and f <sub>comp(IF)</sub> | 6    | -    | 7              |        |

| D/D <sub>RF(REFDIV)</sub> | RF reference divider ratio              | REFDIV = 0                                                  | _    | 65   | _              |        |

|                           |                                         | REFDIV = 1                                                  | _    | 130  | _              |        |

| D/D <sub>IF(REFDIV)</sub> | IF reference divider ratio              | REFDIV = 0                                                  | _    | 1    | _              |        |

|                           |                                         | REFDIV = 1                                                  | _    | 2    | -              |        |

| General                   |                                         |                                                             |      | •    |                |        |

| t <sub>ON</sub>           | turn-on time                            | 90% of the final current                                    | _    | -    | 200            | μs     |

#### Notes

- 1. Measured and guaranteed only on OM 5178 demonstration board.

- 2. This value includes printed-circuit board and balun losses.

- 3. The power level of the spurious signals in this measurement is less than specified under SPUR<sub>P(RFin)</sub>.

- 4. IP2<sub>i</sub> related to an IM2 measurement in low gain mode.

- 5. Voltage gain defined as the differential baseband RMS output voltage (either at pins IA and IB or pins QA and QB measured in standard load) divided by the RMS input voltage at the RF baluns.

- 6. This range is obtained through variation of the external reference resistor.

- 7. Measured at external transmit VCO output.

- 8. This is based on an adjustment in such a way, that a difference of 36 dBc is obtained in the level of the wanted signal at the frequency  $f_{IF} + f_{mod}$  and the level of the signal at the frequency  $3f_{IF} f_{mod}$ , measured at the input of the phase-frequency comparator for IF frequencies of 45.5 and 91 MHz.

# UAA3535HL

## SERIAL TIMING CHARACTERISTICS

Initial parameter values: V\_{CC} = 2.6 V ±5%; T\_{amb} = –30 to +70 °C; unless otherwise specified; see Fig.3.

| SYMBOL             | PARAMETER                             | MIN. | TYP. | MAX. | UNIT |

|--------------------|---------------------------------------|------|------|------|------|

| Serial progra      | amming clock: pin CLK                 | I    | 1    | 1    | 1    |

| t <sub>r</sub>     | rise time                             | -    | 10   | 20   | ns   |

| t <sub>f</sub>     | fall time                             | -    | 10   | 20   | ns   |

| T <sub>cy</sub>    | clock cycle time                      | 200  | -    | _    | ns   |

| Enable prog        | ramming: pin Ē                        |      |      |      |      |

| t <sub>su(E)</sub> | delay to rising clock edge            | 200  | -    | _    | ns   |

| t <sub>h(E)</sub>  | delay from last falling clock edge    | 100  | -    | _    | ns   |

| t <sub>W(E)</sub>  | minimum inactive pulse width          | 4000 | -    | _    | ns   |

| t <sub>su(E)</sub> | enable set-up time to next clock edge | 200  | -    | -    | ns   |

| Register ser       | ial input data: pin DATA              |      |      |      |      |

| t <sub>su(D)</sub> | input data to clock set-up time       | 50   | -    | _    | ns   |

| t <sub>h(D)</sub>  | input data to clock hold time         | 50   | -    | -    | ns   |

Philips Semiconductors

Objective specification

# Low power GSM/DCS/PCS multi-band transceiver

UAA3535HL

\_

2000 Feb 17

# UAA3535HL

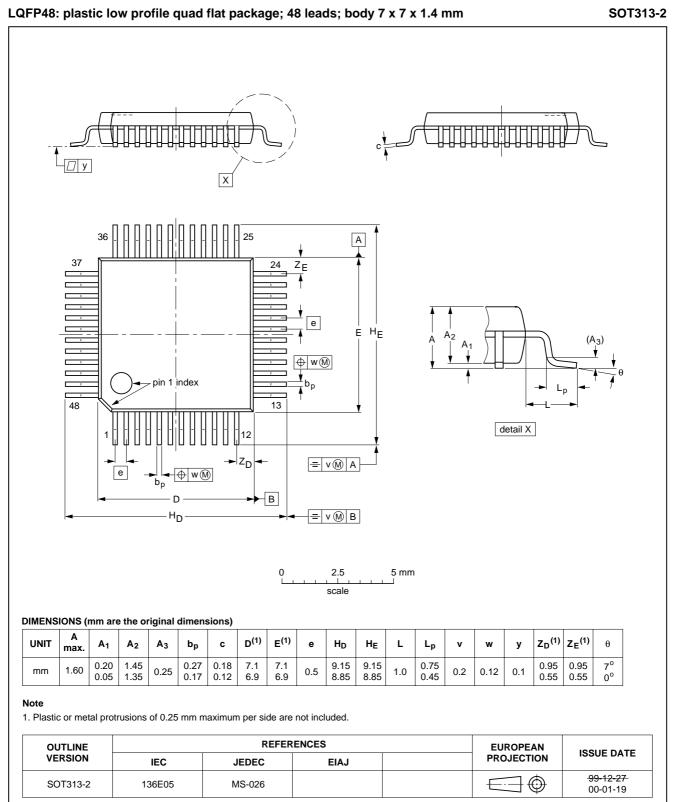

# PACKAGE OUTLINE

# UAA3535HL

## SOLDERING

## Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"Data Handbook IC26; Integrated Circuit Packages"* (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering is not always suitable for surface mount ICs, or for printed-circuit boards with high population densities. In these situations reflow soldering is often used.

## **Reflow soldering**

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, infrared/convection heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 230 °C.

## Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

• Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is **preferred** to be parallel to the transport direction of the printed-circuit board;